MSYS2

--Software Distribution and Building Platform for Windows

MSYS2 is a collection of tools and libraries providing you with an easy-to-use environment for building, installing and running native Windows software.

但实际上,我们可以想见的????????????????????,配置环境想来是令人难受的!

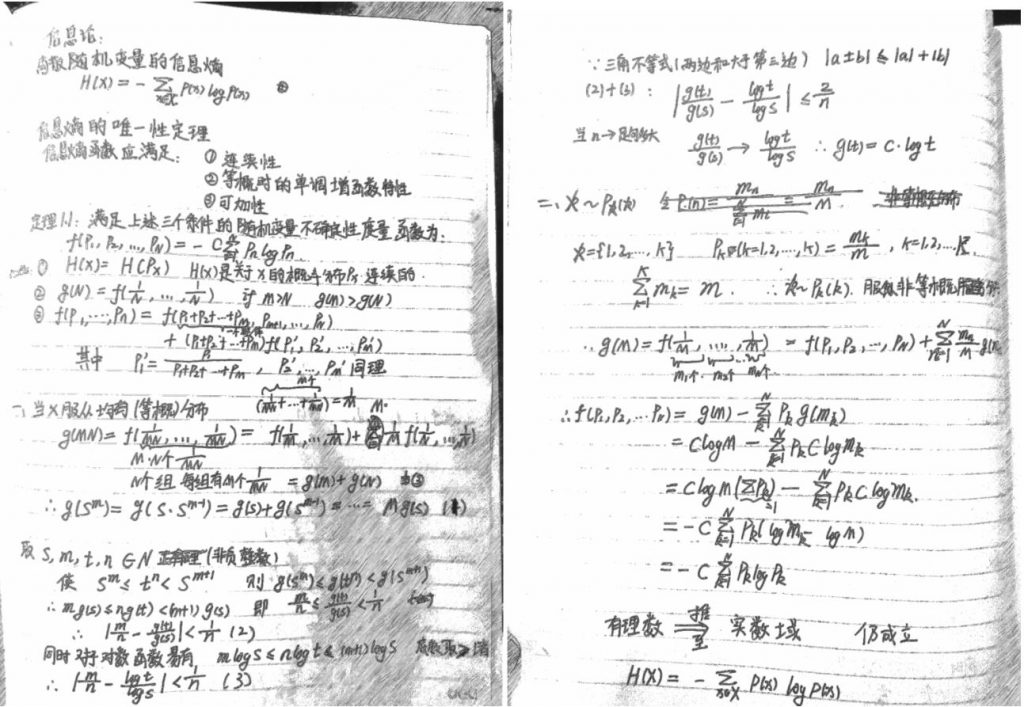

信息熵的唯一性定理(手写-手机处理)

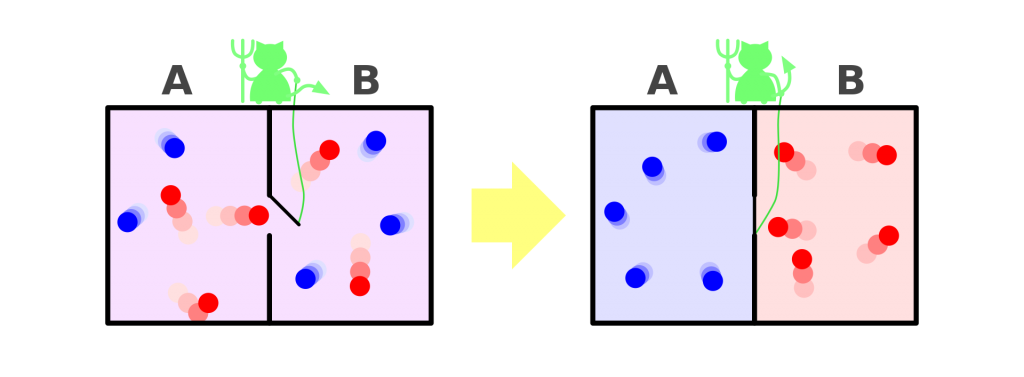

信息熵与热力学熵---麦克斯韦妖佯谬

在小妖观测两个容器内的分子时,便引入了信息熵。

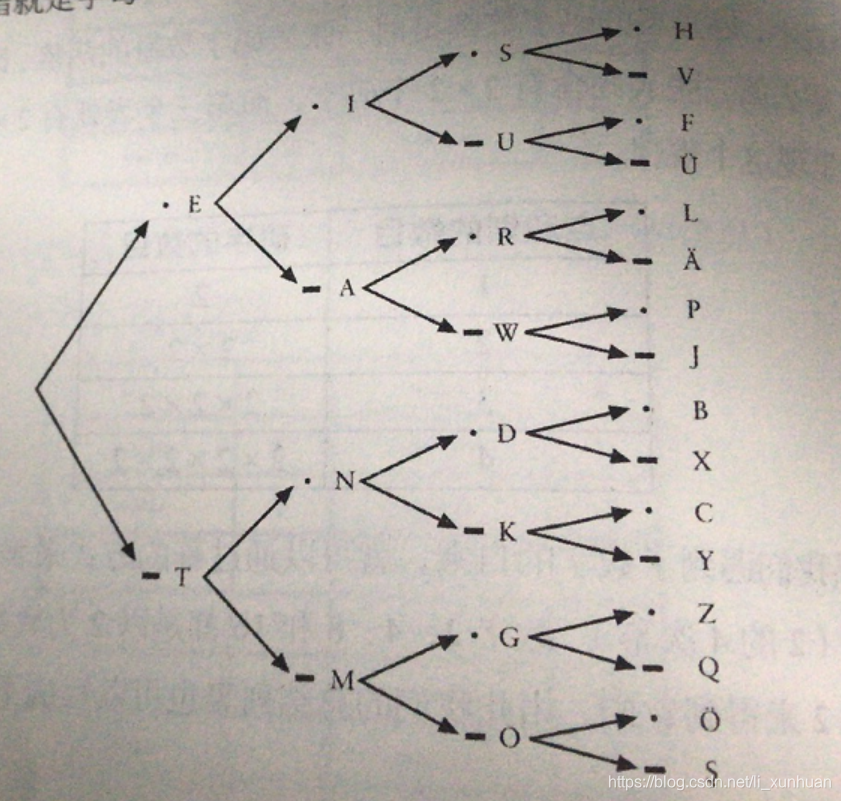

摩尔斯电码的编码

这时一个非奇异码,但不是唯一可译码,想想,可以优化吗?优化成异字头码,用霍夫曼编码来操作?好像不成,这是一种规定好了的编码,优化之后的编码,就不是摩尔斯电码了。

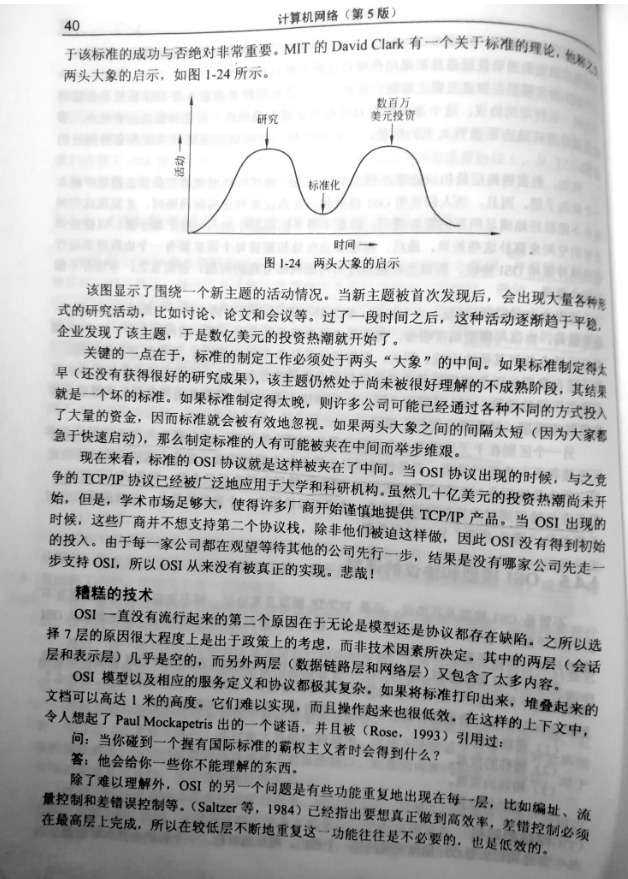

计算机网络第五版--OSI模型和协议的评判-图书链接

百度知道用户:彭咿呀

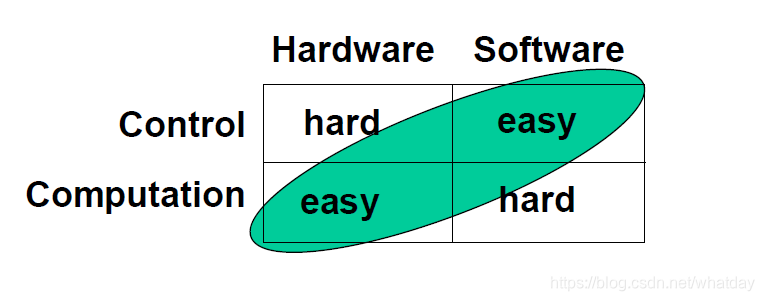

糟糕的提出者:OSI是学者们提出的(面向技术,这也意味着它很复杂,很难应用到实际),TCP则是各大计算机寡头提出(面向实用,简化了很多,直接得到了大量用户群)糟糕的技术:不知道你有没有发现,OSI中的会话和表示层几乎是空的,而数据链路和网络层有包含了太多的东西。它所制定的标准和协议都极其复杂,(据说打印出来能堆1米多)且很多功能重复(如流控和差错控制)

糟糕的实现:TCP/IP协议族早期是作为UNIX的一部分,运行非常好,而且是免费的,这使它迅速在程序员中形成了一个庞大的用户群。而OSI则一直躺在实验室,没接触到群众。

糟糕的政策:当初的学术界都认为OSI由美国军方背景,是美国政府的产物;而TCP是UNIX一部分,这使得很多崇尚自由的欧美程序员彻底爱上了TCP。

https://zhidao.baidu.com/question/2208213838650237668.html

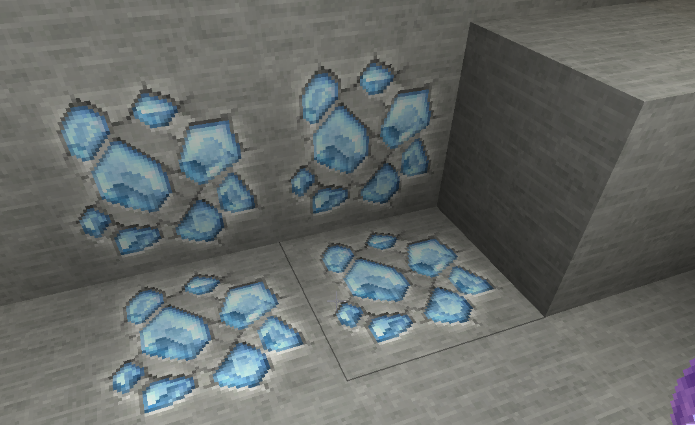

minecraft我的世界--钻石,钻石!

莫言在2012年诺贝尔奖的演讲

点击???? 链接:http://www.liuxue86.com/a/3335761.html 在????????????????